IBM:半導体業界の長老

IBMは、以前と比べると、ずいぶんと規模が小さくなっているかもしれませんが、マネージド サービスとホスティング ビジネスがKyndrylと呼ばれる新会社へ分社化された後には、さらに小さくなりそうです。新たなKyndryl社は、事業規模約190億ドル、顧客数約4,600社、従業員数約9万名という規模になるようです。これにより、IBM本体に残る側では、Power SystemsおよびSystem zプラットフォームに重点が置かれ、ハイブリッド クラウド、人工知能、および量子コンピューティングが全面的に推進されることになるようです。

残る側は、売上高約590億ドル、従業員数約26万名、主要顧客およそ数十万社(直接販売、間接販売を合わせて)を抱えることになります。6年前にSystem x事業が売却され、残りのIBM顧客ベースはかなり縮小しましたが、LenovoへのSystem xの売却を行っても、そうしなかった場合と比べて、IBMの収益性が大幅に向上したとは言えなさそうです。

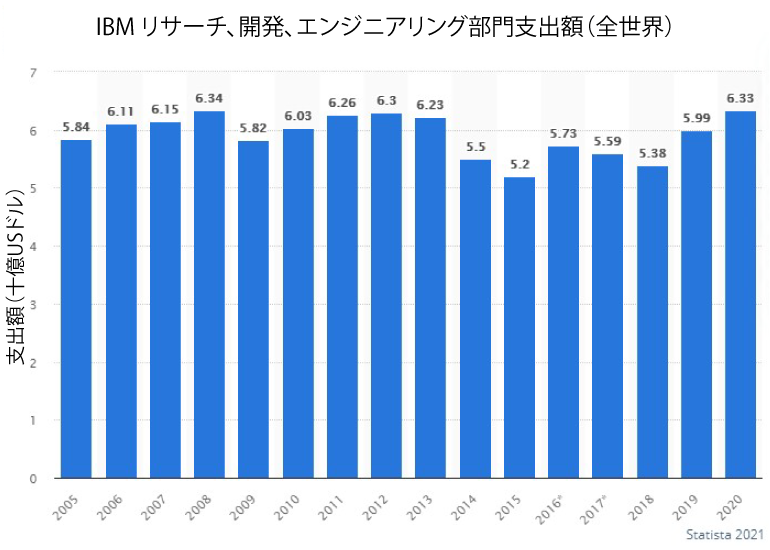

IBMの収益性(短期的な会計上の意味で)が、そう考えられるほど高くない一因は、IBMが研究開発にかなり多大な資金を投じていることにあります。さらに言えば、IBMは事業を売却しても、その投資水準を維持してきたか、あるいは増やすことさえしています(下図参照)。

2000年代中後期には、IBMは今日に比べて25%ほど規模が大きかったものの、2020年に(および2021年は見込み)研究開発に費やされた資金はその当時と同じくらいです。これはムチャなことのようにも思われますが、IBMが学んだことがあるとすれば、そうした研究開発資金のすべてが、同社の特許ポートフォリオを拡大させ続ける元となり、競合企業に技術を売却することでかなりの額を生み出すことができるということです。たとえば、Intelは、今年、両社が結んだパートナーシップ契約の一環で、次世代の半導体製造についてIBMに支援を求めてきたということです。IBMは、何年も前に、同社のマーチャント(外販)およびキャプティブ(内製)用のファウンドリー事業をGlobalFoundries社に売却し、GlobalFoundries社の22ナノメートルおよび14ナノメートル プロセスでPower8およびPower9チップをエッチングしました。7ナノメートルおよび5ナノメートル プロセスではSamsung社と協働しており、実用向け2ナノメートル プロセスの製造では、IntelとSamsungと協働するということです。

先週のThink 2021バーチャル カンファレンスに先立って、この1年間、IBMの舵を執ってきたIBM CEOのArvind Krishna氏に、チップ ビジネスにおける供給不足について少し話を聞かせてもらいました。折しも、それぞれのトランジスタをシュリンクさせることが徐々に難しくなりつつあり、また、シュリンクのたびにトランジスタのコストを低減させ、それによってIT業界全体の経済を回すというのは、もっと難しいことになっています。

IBMが投入しているほどの資金があれば、行えることは非常にたくさんあるため、IBMが、どうして原初的である半導体設計および製造技術に、今もなお投資しているのか疑問に思われるかもしれません。IBM Microelectronicsを売却(ちなみに、実際はGlobalFoundries社にお金を支払って引き継いでもらったというのがより正確です)した理由は、チップ ファブや研究開発に対する支払いから逃れることではなかったのでしょうか。IBMが研究開発を続けてきたことは、おそらく良いことだったのでしょう。なぜなら、IntelとSamsungは、5ナノメートル、3ナノメートル、および2ナノメートル ノードを開発するために、受けられる支援はすべて必要となるからです(後者はIBMのPower10チップおよびz16チップをエッチングする予定であり、おそらくPower11およびPower12チップ、そしてz17およびz18チップについてもそうなるでしょう)。

IBMが開発し終えたこの2ナノメートル テスト チップの詳細については、『The Next Platform』誌に記していますので、そのデータのすべてについて、ここで改めて記すことはしません。以下では、IBM i に関わることで、読者の皆さんに知っておいてもらう必要があることについて記そうと思います。IBMは、フラッシュ メモリー セルを積み重ねるのと同じようにトランジスタを積み重ねる、ナノシートと呼ばれる技術を開発しました。2ナノメートル テスト チップには3層のトランジスタがあり、これは2ナノメートル テクニックと呼ばれています。ただし、これはトランジスタ ゲート サイズが実際に2ナノメートルだからというわけではありません。この3Dテクニックでは、2ナノメートル ゲートでトランジスタをエッチングしていたとした場合に2D平面設計から期待されるトランジスタの速度と集積度と消費電力が実現されるということです(チップ ビジネスではちょっとした言葉のごまかしが行われているようで、そのせいか、ムーアの法則の限界に、実際よりも近付いているような見え方になってしまっています。エンジニアや科学者は不正確さを良しとしませんが、ドラマも好きなようです。不思議です)。

Power Systemsの顧客にとって大事なのは、IBMがSamsungと提携していて、ニューヨーク州アルバニーの同社の技術センターで、7ナノメートル、5ナノメートル、そして現在は2ナノメートル テスト チップを標準的な300mmシリコン ウエハー上ですでに供給してきたということです。そうしたいわゆる2ナノメートル トランジスタは、今年中にビッグ アイアンNUMAマシンで、エントリー マシン向けには来年初めに出荷されるPower10チップで使用されている7ナノメートル プロセス用に、IBMとSamsungが開発した極端紫外線(EUV)リソグラフィーを多くのステップで使用してエッチングされたトランジスタと比べて、45%高速であるか、または同じ速度で使用電力が75%少なくなっています。IBMは、2024年末までには2ナノメートル テクニックが生産されると想定していますが、必ずしもPower11でそれが使用されることになるわけではありません。Power11は、成熟段階の5ナノメートル プロセスとなると私たちは予想しています。しいて推測するとしたら、IBMは一部のトランジスタ粉末を乾燥させておいて、おそらくSamsungとともに、2ナノメートル テクニックを使用してPower12およびz18を製造するでしょう(IBMが言わないからこそ推測するのです)。

先進的なファウンドリーのキャパシティー不足は大きな問題ですが、推測するに、もちろん、お金でIBMが支援することができる問題です。ますます多くの顧客が、ますます少なくなっているファウンドリーを捜し求めるにつれて、最近では、ありとあらゆるサプライ チェーンがチップの供給不足に襲われています。Krishna氏はチップ ビジネスにおける供給不足について尋ねられ、次のように述べています。

「昨今の半導体不足は、非常に困った状況だと思います」とKrishna氏は説明します。「自動車向けチップの不足に大きな注目が集まっており、それは確かに大事な問題ですが、それだけに留まらないのです。不足しているのは自動車向けだけでしょうか。あるいは、メモリー向けのチップも不足しているのでしょうか。そのことでK-12(義務教育)の学生用のラップトップやタブレットに影響が及んでいないでしょうか。あるいは、サーバー向けのチップはどうでしょうか。そして家電製品については全面的です。どこか1つという状況ではなくなっています。人々が求められているのは、私が実に不幸なジレンマと呼んでいるものについての判断です。すなわち、何が優先されるべきなのかということです。そして、それを判断するのは非常に難しいことです。今では、キャパシティーを増やしたい場合、特に、どこか特定の地域により近い場合には、半導体を増産するタイム スケールは、残念ながら、年単位で評価されることになります。月単位ではないのです。ある特定のメーカー向け、ある特定のプラント向けに行われた設計を利用することは、それほど単純なことではでありません。こっちの物を手に取って、どこか他へ持って行って使うというわけにはいかないのです。」

GlobalFoundries社が7ナノメートルEUVプロセスで抱えていた問題のせいでその製造の中止を余儀なくされ、IBMがSamsungの腕の中に飛び込むこととなったことから、他の唯一の選択肢となるのは、地球上で最も多くの先進デバイスを製造していて、過負荷状態になっているTSMC(Taiwan Semiconductor Manufacturing Corp)社だということをIBMは知っておかねばなりません。

将来的には、IBMが、Intelおよび同社のIntel Foundry Servicesマーチャント ファウンドリー事業を支援する態勢を整えることになるのは明らかです。そして、この10年間が終わるまでに、Power11とPower12チップ、そしてz17とz18チップを予定通りに市場に出せるようにするためには、IBMには、チップ製造のための固有のセカンド ソースが必要となってくるのではないでしょうか。このことは、IT業界の人間であれば、誰の目にも明らかなことです。